## E系列模块卡开发指南

# E737

# 目录

| <b>-,</b> | 概述        | _ 3 |

|-----------|-----------|-----|

| =,        | FPGA 开发模式 | _ 3 |

| 三、        | 详细开发介绍    | 4   |

## 一、概述

本指南介绍了E737这张2通道声音振动输出卡的上手开发流程。开发环境为装有Linux RT 环境的 RobustRIO U838。板卡为FPGA开发模式,需要用户先开发FPGA程序,再开发上位机程序实现与板卡的数据 交互,且用户可在FPGA使用DMA的方式实现高速的数据交互速率。

下面先展示程序框图,并在指南后续章节做更为详细的介绍。

## 二、 FPGA 开发模式

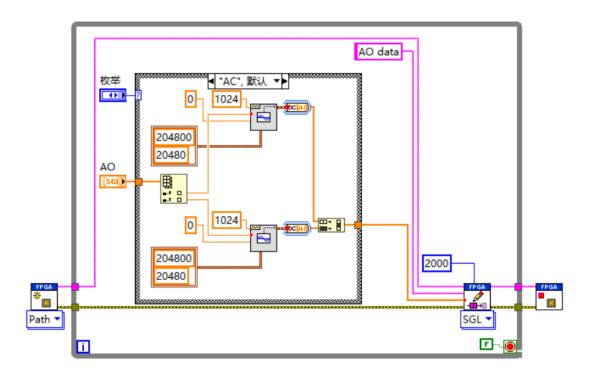

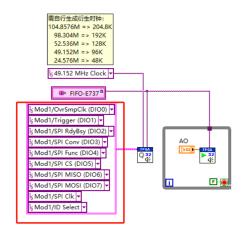

FPGA VI程序框图:

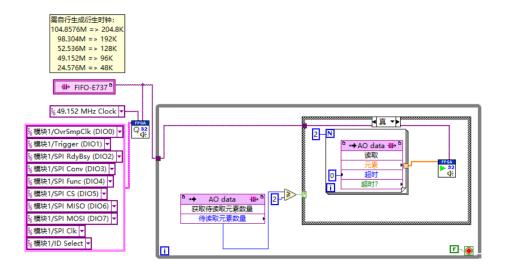

上位机VI程序框图(两种写法):

Α:

B:

#### 详细开发介绍 三、

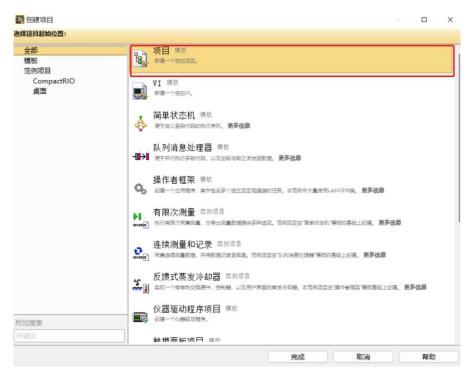

新建LabVIEW工程

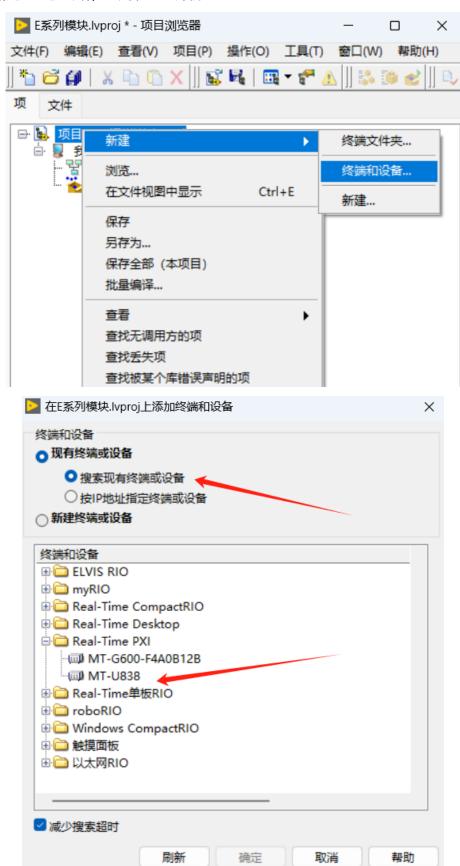

保存工程到相应文件夹下,确定工程名称

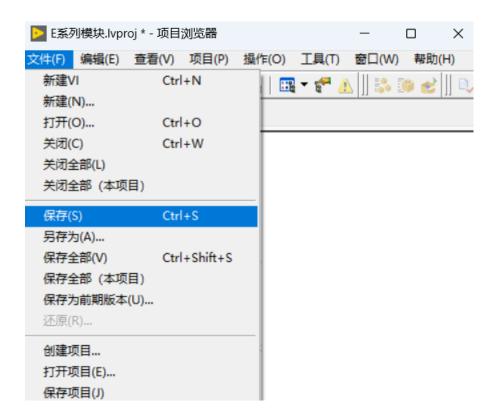

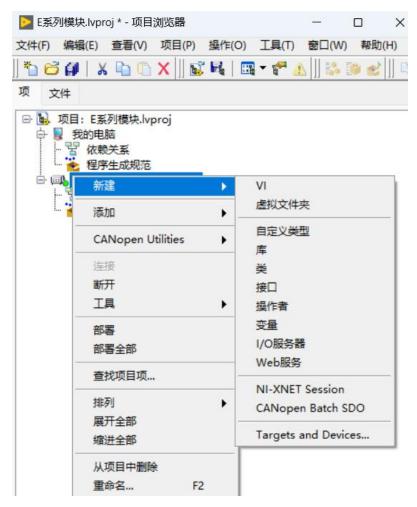

在项目下新建RT主机终端,此处以U838为例:

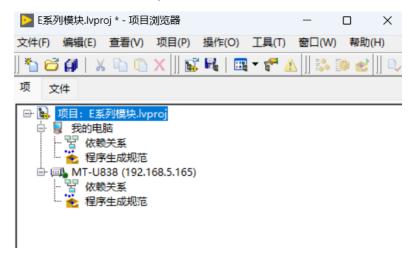

此时RobustRIO通过网络与上位机PC相连,点击确定然后在这里可以看到刚刚新建好的RT终端。

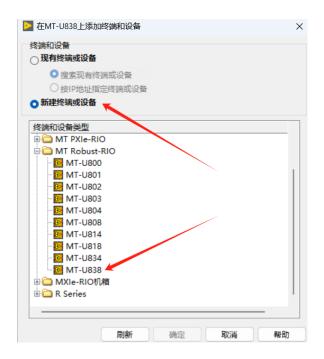

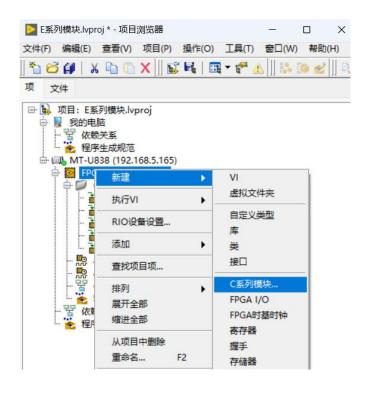

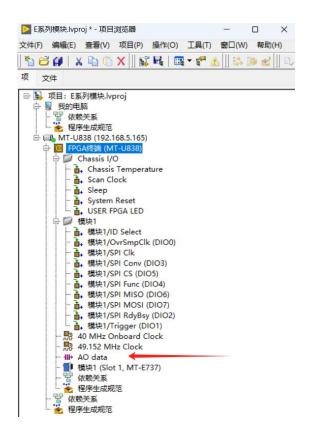

右键RT终端选择连接,连接好之后主机图标上方的指示灯为亮绿色,然后在RT终端下新建MT-U838 FPGA终端:

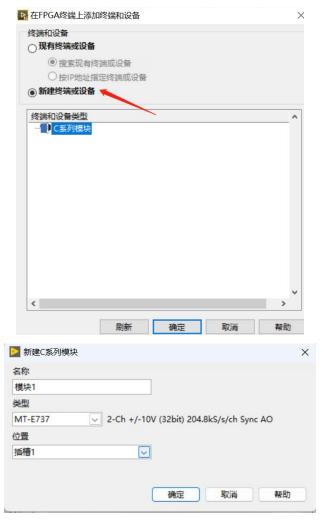

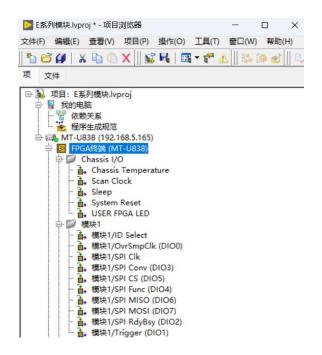

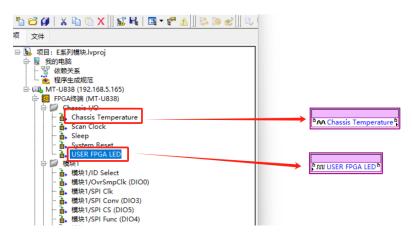

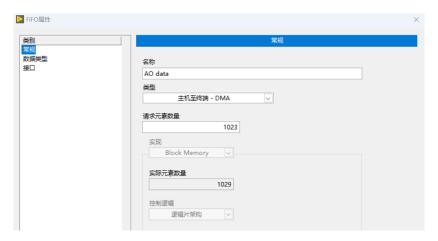

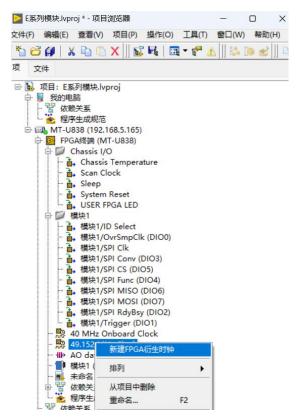

执行好上一步之后在项目浏览器下可以看到刚建好的FPGA终端,然后右键点击FPGA终端新建E737模块 卡,选择相应的槽位(与物理上卡所在槽位一致),然后可在终端下发现相应模块

新建好之后在项目浏览器中会出现E737的模块信息,如下图:

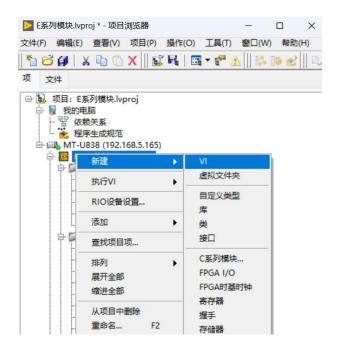

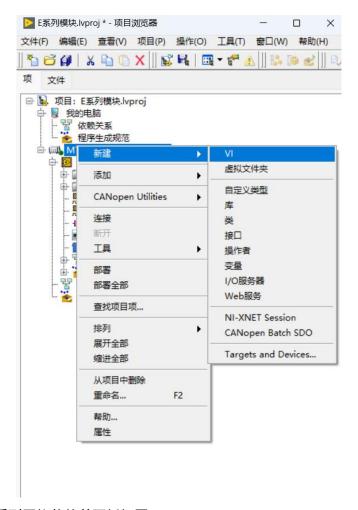

在FPGA终端下新建VI,并保存在项目文件夹下:

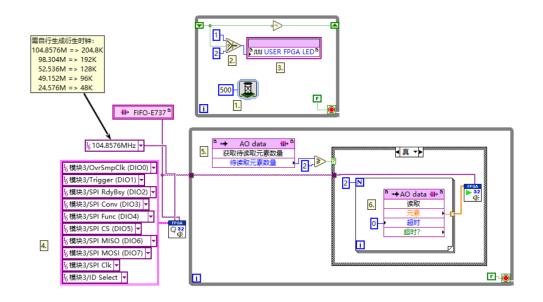

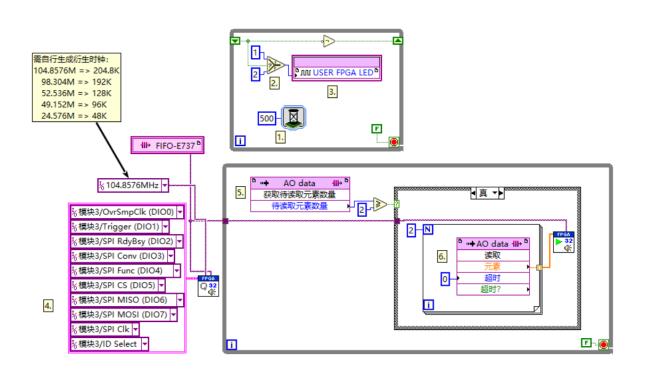

编写FPGA程序, E737 FPGA VI程序框图总览:

程序说明(按程序中所标数字依次说明):

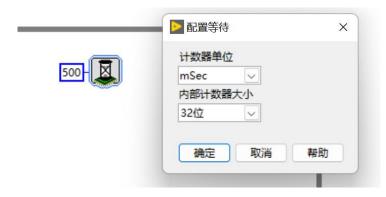

1. 选版下的延时函数,此处用于控制用户灯的闪烁,闪烁间隔500ms,设置方式如下。

- 2. 右键 '比较'选板下的'选择'函数,此处写法用于控制灯闪烁。

- 3. 用户灯节点

用户灯节点在项目浏览器下方Chassis I/0目录下(如下图),在这里同样可以看到常用的温度节点,可以直接将其拖入程序框图中使用,温度节点度数是真实度数的4倍关系,通过除以4运算可得到可用的板载温度数据。用户灯可以呈现两种颜色,分别为:1(颜色1),2(颜色2)

- 4. 模块10接口资源

- 5. FIF0状态节点

- 6. FIF0读取节点

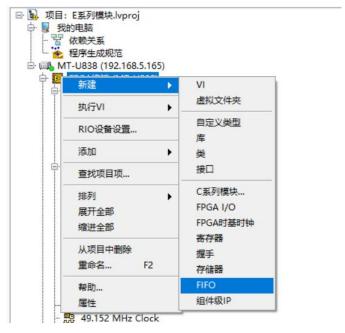

另外,下面的While循环是实现数据采集并通过DMA FIF0的方式上传,新建DMA FIF0的方式: 右键FPGA终端新建FIF0,然后命名此FIF0(此处我将FIF0命名为A0 data)

将类型改为主机至终端(因为E737为输出卡,数据由上位机传向下位机)

并配置FIF0数据类型为上面查看到的板卡接口数据类型

建好之后在项目浏览器中能看到刚刚新建好的FIF0:

然后将MT-E Module选板下的E737模块拖出

依次点击红框内下拉窗口选择对应的10资源,将A0输入控件替换为F1F0节点

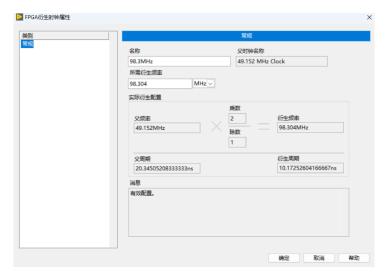

采样率根据时钟不同自行选择,最大支持204.8k,右击FPGA终端下的时钟新建衍生时钟来配置之不同的采样率

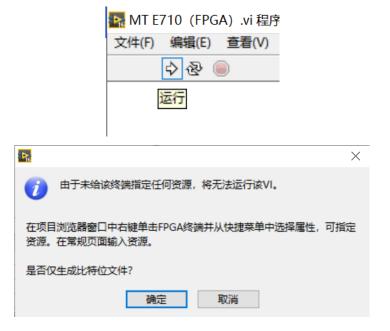

FPGA VI程序写好之后点击左上角运行按钮,点击确认,选择编译器对FPGA程序进行编译,这里需要安装编译器或(注意:目前配套使用的ISE14.7编译器在Win10,Win11系统中经常无法编译,建议在局域网中部署一台win7的电脑,安装好编译器,使用局域网中的编译器进行编译。另外,平均每次编译时长一般在10到40分钟左右,请耐心等待)

推荐使用我们免费提供给客户使用的MT云编译集群服务器,使用方法参照MT-Compile上手指南

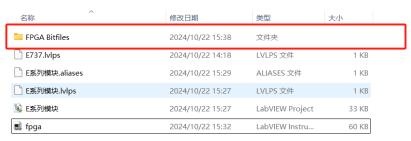

编译好之后,在项目文件夹下会发现刚刚生成好的放置比特文件的文件夹: (编译好之后产生的错误 1003弹窗不必在意,由于FPGA程序无法直接运行导致,请忽略)

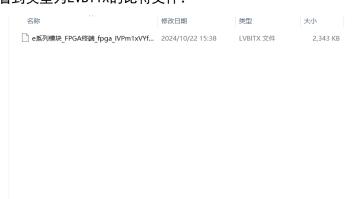

#### 打开文件夹,看到类型为LVBITX的比特文件:

上位机程序开发,在RT终端RobustRI0目录下新建VI,并保存,开始上位机VI程序(Host.vi)编写:

新建和保存好之后可以看到网格状的前面板框图:

Ctrl+E 可以在前面板和程序框图间互相切换:

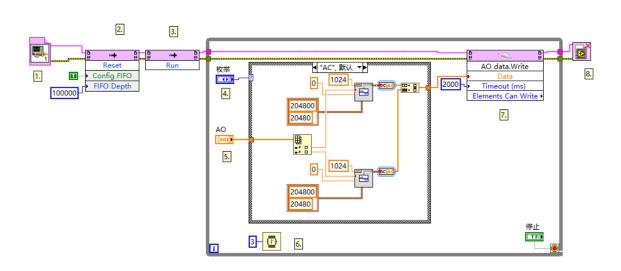

上位机程序的开发提供两种方式,整体的程序框图如下,详细的开发流程参见<u>RobustRIO用户指南</u>中的上位机程序开发章节。

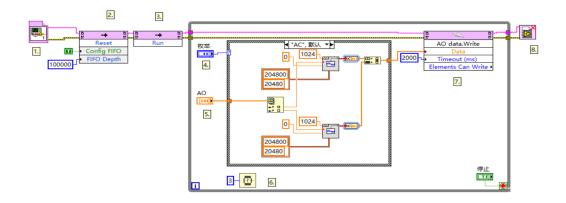

方法A程序框图总貌:

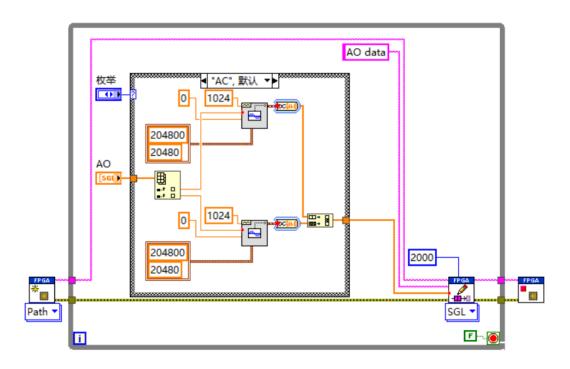

方法B程序框图总貌: